|

www.elektronik.si

Forum o elektrotehniki in računalništvu

|

| Poglej prejšnjo temo :: Poglej naslednjo temo |

| Avtor |

Sporočilo |

aly

Član

Pridružen-a: Tor 28 Sep 2004 14:51

Prispevkov: 9407

Aktiv.: 42.23

Kraj: Kranj - struževo

|

Objavljeno: Tor Dec 19, 2006 11:39 am Naslov sporočila: Objavljeno: Tor Dec 19, 2006 11:39 am Naslov sporočila: |

|

|

Za to rabiš več naslovnih dekoderjev, ki krmilijo enable in/ali reset pin. Podatkovne linije vežeš paralelno. Adresne linije ram-ov tudi vežeš paralelno in ti predstavljajo LSB del naslova. Si predstavljaš ali narišem?

_________________

I'm going to stand outside, so if anyone asks, I'm outstanding  |

|

| Nazaj na vrh |

|

|

Sokrat

Član

Pridružen-a: Čet 25 Avg 2005 11:00

Prispevkov: 5584

Aktiv.: 25.07

|

Objavljeno: Tor Dec 19, 2006 11:56 am Naslov sporočila: Objavljeno: Tor Dec 19, 2006 11:56 am Naslov sporočila: |

|

|

Si predstavljam, rad pa bi videl konkretne vrstice kode, ki se prevedejo - ta del mi povzroca tezave

_________________

Ka ti bo pa torba ce si kupu kolo ? |

|

| Nazaj na vrh |

|

|

BorutS

Član

Pridružen-a: Pet 09 Jun 2006 16:25

Prispevkov: 107

Aktiv.: 0.49

Kraj: Cerklje na Gorenjskem

|

Objavljeno: Tor Dec 19, 2006 2:02 pm Naslov sporočila: Objavljeno: Tor Dec 19, 2006 2:02 pm Naslov sporočila: |

|

|

To lahko narediš na več načinon.

1. v VHDL uporabiš array.... vse ostalo se zgodi ob sintezi - dobiš neodvisno kodo od fpga.

2. preštudiraš datasheet in uporabiš DPR kot bloke, katerim dodaš dekodirno logiko

3. uporabiš IP Coregen

Jaz uporabljam 2. možnost, sicer pa priporočam 3. ker je najenostavnejše in najhitreje. Imaš tudi kar nekaj primerov na xilinx-ovi strani.

LP

Borut

|

|

| Nazaj na vrh |

|

|

fogl

Član

Pridružen-a: Sob 11 Sep 2004 22:37

Prispevkov: 80

Aktiv.: 0.36

Kraj: Radovljica

|

Objavljeno: Sre Dec 20, 2006 11:20 pm Naslov sporočila: Objavljeno: Sre Dec 20, 2006 11:20 pm Naslov sporočila: |

|

|

Berevm vodič o ISE, pa mi pri core generatorju vrže ven to:

Customizing IP...

8.2i - Xilinx CORE Generator IP GUI Launcher I.31(c) 1995-2006 Xilinx, Inc. All rights reserved.Finished Customizing.

Generating IP...

WARNING:sim:226 - The chosen IP does not support a Verilog behavioral model, generating a Verilog structural model instead. Files/Xilinx\coregen\lib\coreutil/jar;C:/Programin thread "main" ERROR:coreutil - An error occurred while running Java. Please examine the console or coregen log file for a specific IP related error.

If there is no specific error the problem may be due to memory limitations. For more information please consult solution record 21955 available from:

http://www.xilinx.com/xlnx/xil_ans_display.jsp?getPagePath=21955WARNING:coreutil:266 - Could not remove outfile.

Finished Generating.

ERROR:sim:57 - Error found during generation

Sem prebral kar piše na njihovi uradni strani...zmanjšal sem ram za javo na minimum (imam 1,5G rama), pa še vedno isto...bral sem da so verzijo ISE 8.1 motili presledki v imenih fajlov (program files), jest imam pa verzijo 8.2, se pravi to ni problem.

Se je še komu to dogodilo? Kaj bi še lahko bilo narobe?

_________________

lp, klemen |

|

| Nazaj na vrh |

|

|

gaborp

Član

Pridružen-a: Sob 16 Jul 2005 9:54

Prispevkov: 63

Aktiv.: 0.28

Kraj: Škofja Loka / Tržič

|

Objavljeno: Čet Dec 21, 2006 10:44 am Naslov sporočila: Objavljeno: Čet Dec 21, 2006 10:44 am Naslov sporočila: |

|

|

Jaz sem imel instalirano verzijo 8.2i v direktoriju Program Files in sem imel probleme s presledki. Pomagala je edino nova instalacija v privzeti direktorij, ki ga ponudi installer.

Nevem pa kakšen error mi je javljalo, tako da se prej prepričaj preden se polotiš nove instalacije.

|

|

| Nazaj na vrh |

|

|

smartgsm

Član

Pridružen-a: Sob 10 Apr 2004 11:54

Prispevkov: 364

Aktiv.: 1.63

|

Objavljeno: Čet Dec 21, 2006 4:44 pm Naslov sporočila: WEB LINK začetki Objavljeno: Čet Dec 21, 2006 4:44 pm Naslov sporočila: WEB LINK začetki |

|

|

Pozdravljeni

instaliral sem si web link.

Sedaj pa se ubadam z trdim začetkom.

Za začetek bi rad sestavil enostavno logično vezje z recimo AND vrati.

Prebral oz. preletel sem skoraj vsa navodil na njihovi spletni strani.

Mislim pa programirat v VHDL.

Cilj pa je za začetek izdelat 24 bitne up/down števce.

problem nastane pri simulaciji.

ALI lahko nekdo napiše/opise postopek za enostaven primer.

Od novega projekta do zaključka oz simulacije.

|

|

| Nazaj na vrh |

|

|

Sokrat

Član

Pridružen-a: Čet 25 Avg 2005 11:00

Prispevkov: 5584

Aktiv.: 25.07

|

Objavljeno: Čet Dec 21, 2006 5:45 pm Naslov sporočila: Objavljeno: Čet Dec 21, 2006 5:45 pm Naslov sporočila: |

|

|

Ce imas Xilinxov starter kit (skatlo s CDji, plosco, papirji, itd.), potem je zraven knjizica Introduction to Programmable Logic, ki ocitno ne obstaja v PDFju (vsaj jaz je na hitro nisem uspel najti). Tam notri je razlozeno tocno to, kar isces, le da je primer precej neuporaben (gre ravno za en stevec, ampak za tako malenkost ne rabi clovek CLPDja/FPGAja - lahko bi dali boljse primere  ). ).

Morda ti bo pomagal kaksen primer s te strani - tam so med ostalim tudi AND vrata in genericen primer stevca (ki je lahko tudi 24-biten, ce mu tako nastavis sirino). O simulaciji na tej strani sicer ne pise nic.

_________________

Ka ti bo pa torba ce si kupu kolo ? |

|

| Nazaj na vrh |

|

|

smartgsm

Član

Pridružen-a: Sob 10 Apr 2004 11:54

Prispevkov: 364

Aktiv.: 1.63

|

Objavljeno: Pet Dec 22, 2006 9:06 am Naslov sporočila: FPGA Objavljeno: Pet Dec 22, 2006 9:06 am Naslov sporočila: FPGA |

|

|

Ja poznam ta primer.

Zal pa je nekaj nastavitev potrebno narediti vmes, ki notri niso vpisane.

Pa se daj malo lovim.

Bom še malo poiskušal.

Grega

|

|

| Nazaj na vrh |

|

|

seba001

Član

Pridružen-a: Pon 22 Maj 2006 14:04

Prispevkov: 19

Aktiv.: 0.09

|

Objavljeno: Pon Feb 26, 2007 9:21 pm Naslov sporočila: Objavljeno: Pon Feb 26, 2007 9:21 pm Naslov sporočila: |

|

|

Uporabljam Xilinx ISE 9.

Zanima me, kako in kdaj v programski kodi določim da je neka spremenljivka tipa reg.

Ali moram to narediti že na začetku, ko definiram vhode in izhode ali pozneje v programu?

lp

|

|

| Nazaj na vrh |

|

|

commander29

Član

Pridružen-a: Pon 20 Nov 2006 15:24

Prispevkov: 47

Aktiv.: 0.22

|

Objavljeno: Sre Avg 08, 2007 9:42 am Naslov sporočila: Objavljeno: Sre Avg 08, 2007 9:42 am Naslov sporočila: |

|

|

Pozdravljeni

Začel sem se ukvarjati z FPGA-ji in notranjost spoznal s pomočno NanoBoard-a NB1. Sedaj pa sem prišel do točke, kjer bo potrebno narediti samostojno vezje.

HW bo vseboval 2xSRAM (512kbitx8-), LPC2138, Flash (4Mbit), led controlerje in XC3S200 (mogoče 50 ali 400 ampak vse odvisno z velikostjo na koncu), in seveda Platform Flash XCF02.

Sam uporabljam Altium Designer in Webpack 9.1i.

Imam nekaj vprašanj, na katere sem naletel med "designiranjem".

1. VCCO_X (X=BANKA). Ali s napajanjem teh dveh pinov na eni banki določimo output (ali tudi input) logične napetosti na vseh I/O pinih na tej banki ali moram paziti še na kaj?

2. Na tem forumu sem prebral tudi, da se morajo napajalne napetosti (SPARTAN 3 ima tri +1V2, +2V5 in 3V3 prižigati v zaporedju). Če je temu tako, v kakšnem?

3. Povezava Boot Flash-a in FPGA-ja?

4. M0, M1, M2:

Prebral sem User Guide, Generation Configuration User Guide, pa še vedno mi ni čisto jasno kako naj jih nastavim.

Kaj bi rad imel:

Rad bi preko JTAG-a programiral direktno na FPGA (development stage) in rad bi Preko JTAG-a programiral Boot Flash direktno.

Rad bi potrditev tega:

Če nastavim vse tri (M0, M1, M2) na GND pomeni da bo FPGA čakal na Flash, če pa nastavim M2 in M0 na 2V5 in M1 na GND pa pomeni da bo FPGA nastavljen za prenos iz PC-ja.

|

|

| Nazaj na vrh |

|

|

aly

Član

Pridružen-a: Tor 28 Sep 2004 14:51

Prispevkov: 9407

Aktiv.: 42.23

Kraj: Kranj - struževo

|

Objavljeno: Sre Avg 08, 2007 5:34 pm Naslov sporočila: Objavljeno: Sre Avg 08, 2007 5:34 pm Naslov sporočila: |

|

|

| commander29 je napisal/a: |

| 1. VCCO_X (X=BANKA). Ali s napajanjem teh dveh pinov na eni banki določimo output (ali tudi input) logične napetosti na vseh I/O pinih na tej banki ali moram paziti še na kaj? |

Po moje je zadosti, če jih povežeš na ustrezno napajanje. Jaz imam vse na 3.3V.

Pazi na zadostno število kondenzatorjev.

Glej datasheet!

| commander29 je napisal/a: |

| 2. Na tem forumu sem prebral tudi, da se morajo napajalne napetosti (SPARTAN 3 ima tri +1V2, +2V5 in 3V3 prižigati v zaporedju). Če je temu tako, v kakšnem? |

Jaz imam vse vezano paralelno in deluje - ob počasnem dvigu napajalne napetosti. Če vklopim na hitro - vtaknem konektor, gre vezje v latch-up in potegne 1A toka (limita regulatorja).

Preberi datasheet!!

| commander29 je napisal/a: |

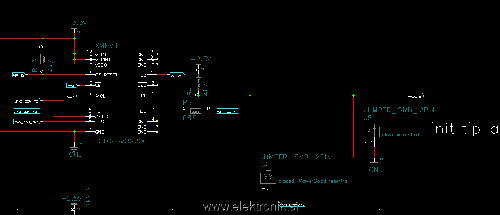

| 3. Povezava Boot Flash-a in FPGA-ja? |

preberi

DS123 - Platform Flash In-System Programmable Configuration PROMs

in

XAPP453 - The 3.3V Configuration of Spartan-3 FPGAs

jaz sem naredil po shemi Figure 4 v drugem dokumentu in deluje ok.

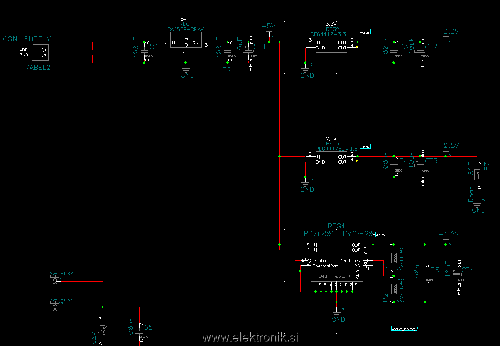

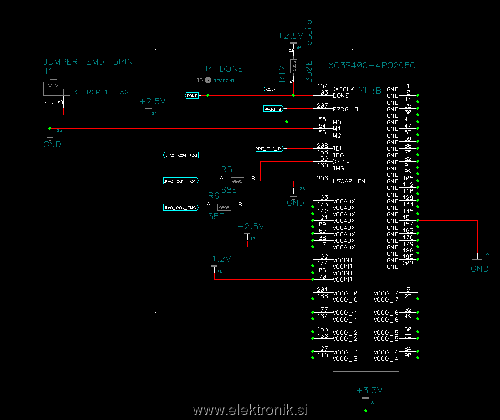

Glej priponko.

In ne pozabi na "Rpar" upor na 2.5V napajalni liniji!

| commander29 je napisal/a: |

| 4. M0, M1, M2: |

preberi

UG332 - Spartan-3 Generation Configuration User Guide

| commander29 je napisal/a: |

| Rad bi preko JTAG-a programiral direktno na FPGA (development stage) in rad bi Preko JTAG-a programiral Boot Flash direktno. |

Če pravilno povežeš JTAG, lahko programiraš oba hkrati.

Zraven lahko dodaš tudi LPC in še kaj, kar ima JTAG.

| commander29 je napisal/a: |

| Če nastavim vse tri (M0, M1, M2) na GND pomeni da bo FPGA čakal na Flash, |

Ne bo ga nič čakal, ampak bo FPGA generiral clock (CCLK), prebral podatke iz flash-a in začel s startup sekvenco.

| commander29 je napisal/a: |

| če pa nastavim M2 in M0 na 2V5 in M1 na GND pa pomeni da bo FPGA nastavljen za prenos iz PC-ja. |

ja.

FPGA bo čakal na externi clock preko JTAG-a.

Pravtako mora biti v .bit fajlu nastavljen pravi startup clock - nastaviš ga pod Generate Programming File.

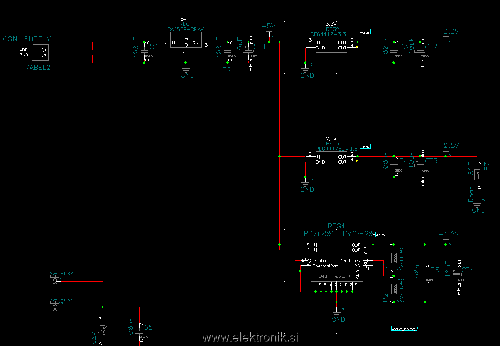

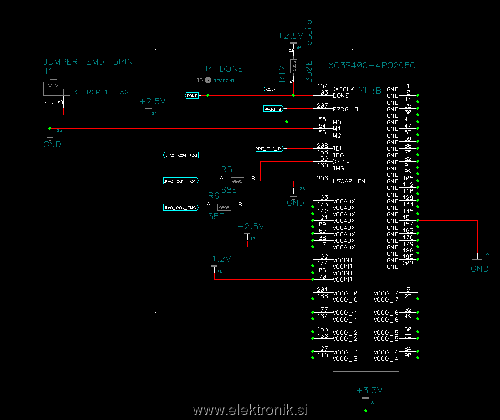

Dodal sem ti shematike, kako sem jaz naredil.

Ne zanašaj se na moje vezje - delaj po uradni dokumentaciji.

| Opis: |

|

| Velikost datoteke: |

12.29 KB |

| Pogledana: |

36 krat |

|

| Opis: |

|

| Velikost datoteke: |

19.77 KB |

| Pogledana: |

18 krat |

|

| Opis: |

|

| Velikost datoteke: |

23.98 KB |

| Pogledana: |

25 krat |

|

_________________

I'm going to stand outside, so if anyone asks, I'm outstanding  |

|

| Nazaj na vrh |

|

|

Glitch

Član

Pridružen-a: Pet 07 Apr 2006 11:40

Prispevkov: 1477

Aktiv.: 6.73

|

Objavljeno: Sre Avg 08, 2007 11:05 pm Naslov sporočila: Objavljeno: Sre Avg 08, 2007 11:05 pm Naslov sporočila: |

|

|

Glede napajanja moras obvezno pogledat v datasheet. Neketeri cipi zahtevajo sekvencen vklop napajanja, drugi pac ne.

Rpar je potreben samo pri dolocenih napajalnikih, ki ne trpijo vsiljevanja visje napetosti na izhodu.

Kot pise v datasheetu ima vsaka banka svoje napajanje. To je logicno, saj lahko na eni banki sofiras z CMOS33 nivoji, na drugi pa sofiras LVDS25.

Aly, ali si ze poskusil povezati FPGA in kaksen drug cip serijsko preko JTAG linij? Kot berem na internetu je ta JTAG en "kr nekaj" v takih primerih in ne deluje, tako kot bi moral.

|

|

| Nazaj na vrh |

|

|

aly

Član

Pridružen-a: Tor 28 Sep 2004 14:51

Prispevkov: 9407

Aktiv.: 42.23

Kraj: Kranj - struževo

|

Objavljeno: Sre Avg 08, 2007 11:28 pm Naslov sporočila: Objavljeno: Sre Avg 08, 2007 11:28 pm Naslov sporočila: |

|

|

Takšne multidrop verižne JTAG povezave še nisem preizkušal, ker nisem imel prilike. FPGA in PROM deluje 100%. Moral bi priključit eno LPC plato na obstoječi JTAG vmesnik in videt, če se zmenijo. Seveda bi rabil BSDL opis LPC-ja. Če taka vezava dela ok, bi moralo delovati tudi v verigi. Je za poskusiti.

Hmmm .. AVRji imajo tudi JTAG. Bom enega AVRja zakuril ob priliki. JTAG pa je menda standardizirana zadeva in bi morale biti reči kompatibilne...

| Glitch je napisal/a: |

| Rpar je potreben samo pri dolocenih napajalnikih, ki ne trpijo vsiljevanja visje napetosti na izhodu. |

In FPGA bo tudi hvaležen, če ne bo imel 3.3V konic na 2.5V napajanju (skozi zaščitne diode).

_________________

I'm going to stand outside, so if anyone asks, I'm outstanding  |

|

| Nazaj na vrh |

|

|

Glitch

Član

Pridružen-a: Pet 07 Apr 2006 11:40

Prispevkov: 1477

Aktiv.: 6.73

|

Objavljeno: Čet Avg 09, 2007 9:09 am Naslov sporočila: Objavljeno: Čet Avg 09, 2007 9:09 am Naslov sporočila: |

|

|

No, ravno to je tisto, zadeve bi morale biti kompatibilne. JTAG je bil namenjen testiranju povezav med cipi in ne programiranju. Tako pa nimajo vsi enako implementirane verige, zadeva ne deluje. Vsekakor za probat, vendar kot sem ze rekel, rezultati ostalih so bolj slabi.

| Citiram: |

| In FPGA bo tudi hvaležen, če ne bo imel 3.3V konic na 2.5V napajanju (skozi zaščitne diode). |

Ja, do tega pride, ce mu silis napacno napetost na napacne pine (JTAG). V normalnih pogojih tega pojava ni. Kot sem napisal: doloceni regulatorji tega ne prenesejo (reverse current).

|

|

| Nazaj na vrh |

|

|

commander29

Član

Pridružen-a: Pon 20 Nov 2006 15:24

Prispevkov: 47

Aktiv.: 0.22

|

Objavljeno: Čet Avg 09, 2007 10:27 am Naslov sporočila: Objavljeno: Čet Avg 09, 2007 10:27 am Naslov sporočila: |

|

|

| Hvala obema za hiter odziv

|

|

| Nazaj na vrh |

|

|

|

|

Ne, ne moreš dodajati novih tem v tem forumu

Ne, ne moreš odgovarjati na teme v tem forumu

Ne, ne moreš urejati svojih prispevkov v tem forumu

Ne, ne moreš brisati svojih prispevkov v tem forumu

Ne ne moreš glasovati v anketi v tem forumu

Ne, ne moreš pripeti datotek v tem forumu

Ne, ne moreš povleči datotek v tem forumu

|

Uptime: 68 dni

Powered by phpBB © 2001, 2005 phpBB Group

|