|

www.elektronik.si

Forum o elektrotehniki in računalništvu

|

| Poglej prejšnjo temo :: Poglej naslednjo temo |

| Avtor |

Sporočilo |

hribo

Član

Pridružen-a: Sob 12 Nov 2011 13:38

Prispevkov: 150

Aktiv.: 0.85

Kraj: Domžale

|

Objavljeno: Pet Jan 13, 2012 9:12 pm Naslov sporočila: Objavljeno: Pet Jan 13, 2012 9:12 pm Naslov sporočila: |

|

|

Ja sedaj vidim, da je to res, da je nakup že izdelanega najbolj optimalna izbira.

Kar se projektov tiče, se bom okvarjal z LED zaslonom, mislim da bo ta projekt za začetek dovolj velik zalogaj da bom nekaj znanja odnesel. Zgled bom vzel s tem projektom.

Potem bo mogoče sledil še kakšen projekt, ampak tisti končni cilj katerega bi rad dosegel, je narediti DVB-T sprejemnik. Vem da bom potreboval kakšen LNA, pa modulator pa ADC, in seveda naštudirati kako se poteka dekodiranje digitalnega signala.

Upam da sedaj razumete zakaj sem tlačil v vezje DDR, in zakaj sem razmišljav o povezavi FPGA ARM.

Moj končni cilj je zame velik izziv, prosim da mi ne noben ne reče, da se mi bolj splača DVB-T sprejemnik kupit v trgovini, ker se dobro zavedam tega dejstva.

Sedaj pa imam pa vprašanja na katerega upam, da mi biste znali pomagat odgovorit, katera razvojna plata bi zmogla to izvesti?

_________________

Failing to plan is planning to fail. |

|

| Nazaj na vrh |

|

|

aly

Član

Pridružen-a: Tor 28 Sep 2004 14:51

Prispevkov: 9407

Aktiv.: 38.07

Kraj: Kranj - struževo

|

Objavljeno: Pet Jan 13, 2012 9:36 pm Naslov sporočila: Objavljeno: Pet Jan 13, 2012 9:36 pm Naslov sporočila: |

|

|

U

Ja, projekt. Konkreten.

Plato boš po mojem rabil kar dobro.

A to boš delal za diplomsko ali magisterij?

V laboratoriju LNIV na FE so se dosti ukvarjali z obdelavo video slike. Mogoče boš tam našel kak napotek za naprej, potem ko ti bodo enostavni programi že mala malica.

Vsekakor pa ne bi že na tej točki gledal za "ta hudo" plato, ki jo boš rabil, temveč začni z eno najcenejšo. Recimo 60 eur, kot sem ti predlagal. To je majhen denar. Pa še prodaš jo lahko na koncu.

Potem, ko boš zadeve naštudiral, pa boš mogoče že znal oceniti, kaj vse rabiš za DVB-T.

_________________

I'm going to stand outside, so if anyone asks, I'm outstanding  |

|

| Nazaj na vrh |

|

|

chaos

Član

Pridružen-a: Sob 16 Sep 2006 22:12

Prispevkov: 1063

Aktiv.: 4.46

Kraj: Zagorje ob Savi

|

Objavljeno: Pet Jan 13, 2012 9:45 pm Naslov sporočila: Objavljeno: Pet Jan 13, 2012 9:45 pm Naslov sporočila: |

|

|

Uf, večleten projekt torej

Za začetek naštudiraj DVBT standard, ker boš moral sam izdelati demodulator / dekoder za sam signal - tega ni na nobenem FPGA boardu. Najboljša varianta bi bila, da bi ta del kar izpulil iz kakšnega že narejenega DVBT sprejemnika, ker za takšne visokofrekvenčne stvari dizajnirat res rabiš znanje in izkušnje.

Izvorno kodiranje avdio-video signala je MPEG4, to je pa drugi večji problem. MPEG4 je precej zahteven algoritem, ki ga sploh ne boš spravil v kakšen manjši FPGA. Sam sem nekaj delal na MPEG2, ki rabi vsaj pribl. 20k Alterinih LE (pribl. 16k Xilinx-ovih). MPEG4 je občutno bolj kompleksen, jaz bi rekel, da rabiš vsaj 50k, raje 70k gate FPGA. Tukaj gre pa že za precej dražje stvari.

Če res hočeš to realizirati, ti svetujem, da si, kot prvo, nabaviš en poceni FPGA board in začneš trenirati Verilog oz. VHDL. Vzporedno s tem lahko začneš pisati svoj MPEG4 dekoder v C-ju, saj boš samo tako dovolj razumel algoritem, da ga boš lahko kasneje spravil v FPGA.

Nočem ti ubijati sanj, a žal je takšno kompleksno stvar spraviti v FPGA je tudi za izkušenega vsaj pol-letno opravilo (govorim o MPEG2, MPEG4 zahteva verjetno še enkrat toliko časa.)

No, če se boš res lotil, ti z veseljem pomagam, če se ti bo ustavilo (in če bom zmožen  ). To mislim glede FPGA kode, glede vhodnega dela po pravici povedano nimam pojma, pa sem iz smeri telekomunikacije ). To mislim glede FPGA kode, glede vhodnega dela po pravici povedano nimam pojma, pa sem iz smeri telekomunikacije

Tukaj lahko začneš brati, za približno predstavo.

LP!

|

|

| Nazaj na vrh |

|

|

hribo

Član

Pridružen-a: Sob 12 Nov 2011 13:38

Prispevkov: 150

Aktiv.: 0.85

Kraj: Domžale

|

Objavljeno: Pet Jan 13, 2012 9:56 pm Naslov sporočila: Objavljeno: Pet Jan 13, 2012 9:56 pm Naslov sporočila: |

|

|

Delal iz te teme ne bom ne diplomsko ne magisterija, vsaj zaenkrat ne računam na kaj takega. Res pa je, da študiram telekomunikacije. V FPGA-jih vidim prihodnost in ker na faksu na žalost ne delamo nič s tega področja, vsaj na moji smeri ne.

Ja nabrš bom res začel s kakšno manjšo razvojno plato, moram še pogledat druge variante, in da zavedam se da bom imel težavno pot, toda kaj pa je v življenju lahkega. Kot bi rekel en profesor s faksa....Tako pač je.

Še neki me zanima, nekatre firme ponujajo študentom cenejše razvojna orodja ali ima FE s kakšno firmo takšen dogovor?

_________________

Failing to plan is planning to fail. |

|

| Nazaj na vrh |

|

|

chaos

Član

Pridružen-a: Sob 16 Sep 2006 22:12

Prispevkov: 1063

Aktiv.: 4.46

Kraj: Zagorje ob Savi

|

Objavljeno: Pet Jan 13, 2012 10:28 pm Naslov sporočila: Objavljeno: Pet Jan 13, 2012 10:28 pm Naslov sporočila: |

|

|

Poskusi z Terasic, mislim, da samo pošlješ kopijo študentske izkaznice.

LP!

|

|

| Nazaj na vrh |

|

|

hribo

Član

Pridružen-a: Sob 12 Nov 2011 13:38

Prispevkov: 150

Aktiv.: 0.85

Kraj: Domžale

|

Objavljeno: Sob Feb 11, 2012 3:15 pm Naslov sporočila: Objavljeno: Sob Feb 11, 2012 3:15 pm Naslov sporočila: |

|

|

Zdravo,

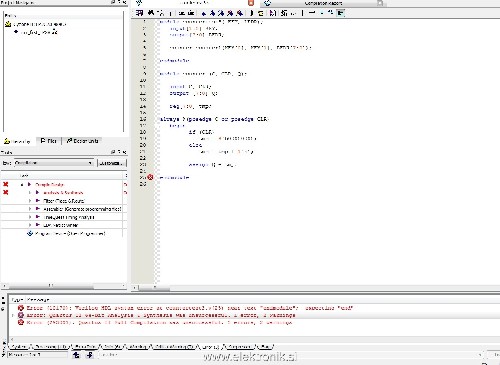

sedaj imam doma svojo razvojno ploščico DE1, toda na žalost se mi je zataknilo že pri prvo stvavri, ki sem jo pisal, sledik sem navodilom ki sme ji našel na youtubu ampak na žalost, mi Quartus ne compila. Že nekaj ur stojim pri tem problemu ali mi zna kdo pomagati?

Hvala za pomoč.

| Opis: |

| koda, napisana v verilogu |

|

| Velikost datoteke: |

203.01 KB |

| Pogledana: |

34 krat |

|

_________________

Failing to plan is planning to fail. |

|

| Nazaj na vrh |

|

|

GopherB

Član

Pridružen-a: Čet 10 Mar 2011 11:44

Prispevkov: 90

Aktiv.: 0.49

Kraj: Lj

|

Objavljeno: Sob Feb 11, 2012 3:26 pm Naslov sporočila: Objavljeno: Sob Feb 11, 2012 3:26 pm Naslov sporočila: |

|

|

| Ali ti še kaj bolj podrobno obrazloži errorje?

|

|

| Nazaj na vrh |

|

|

RGorazd

Član

Pridružen-a: Čet 20 Maj 2004 15:57

Prispevkov: 1717

Aktiv.: 6.95

Kraj: Ig

|

Objavljeno: Sob Feb 11, 2012 3:27 pm Naslov sporočila: Objavljeno: Sob Feb 11, 2012 3:27 pm Naslov sporočila: |

|

|

Ne poznam VHDL, vendar ti že sam kompajler pravi, da ti manjka v zadnjem modulu nekje konec. Sklepam, da če nekaj začneš z begin, potem moraš to nekje tudi končati. Isti princip je v Cju...samo da imaš namesto begin { in namesto end }.

Lp G

_________________

.

._. _ _ ._. _.__. _|

[ (_](_)[ (_] /_(_]

._| |

|

| Nazaj na vrh |

|

|

chaos

Član

Pridružen-a: Sob 16 Sep 2006 22:12

Prispevkov: 1063

Aktiv.: 4.46

Kraj: Zagorje ob Savi

|

Objavljeno: Sob Feb 11, 2012 3:45 pm Naslov sporočila: Objavljeno: Sob Feb 11, 2012 3:45 pm Naslov sporočila: |

|

|

Tako je, pred endmodule dodaj še en end.

Drugače dobra izbira boarda - imam sam istega  Za tako ceno se res ne da dobiti kaj približno enako dobrega. Če boš rabil kakšno pomoč, kar vprašaj. Za tako ceno se res ne da dobiti kaj približno enako dobrega. Če boš rabil kakšno pomoč, kar vprašaj.

LP!

|

|

| Nazaj na vrh |

|

|

hribo

Član

Pridružen-a: Sob 12 Nov 2011 13:38

Prispevkov: 150

Aktiv.: 0.85

Kraj: Domžale

|

Objavljeno: Sob Feb 11, 2012 4:52 pm Naslov sporočila: Objavljeno: Sob Feb 11, 2012 4:52 pm Naslov sporočila: |

|

|

Zdravo, end je bila prva stvar ki sem jo dopisal zraven ampak to ne reši problema ....stric, ki je pisal ta program link za youtubu, ga ni imel, njemu je kompilalo brez problema, res pa je da je imel verzijo 7.2 jaz pa uporabljam 11.1..zanima me kako se definira številke v verilogu, vrstica 19 in 20, kakšna apostrofa mora biti?

@ chaos ja kar nekaj časa sem namenil izbiri svojega boarda, ampak ko sem najdel tole izbira ni bila več težka.

_________________

Failing to plan is planning to fail. |

|

| Nazaj na vrh |

|

|

Musty

Član

Pridružen-a: Sob 28 Apr 2007 8:54

Prispevkov: 1575

Aktiv.: 6.82

Kraj: Rače

|

Objavljeno: Sob Feb 11, 2012 4:55 pm Naslov sporočila: Objavljeno: Sob Feb 11, 2012 4:55 pm Naslov sporočila: |

|

|

Kot so že omenili, ti manjka end pred endmodule.

Verilog v Quartusu včasih potrebuje še bolj eksplicitno določene begin/end definicije z poimenovanjem le teh. V primeru je nekaj poimenovanih in nekaj nepoimenovanih, vsekakor je dobra praksa kar poimenovat zadeve torej: begin:Nekaj / end:Nekaj

| Koda: |

///////////////////////////////////////////////

// Design unit : fir9

// File name : fir.sv

// Description : firN filter, with slight modification can be used for N taps

// Author : Musti

// Version : 3.0

// Quartus compatible

////////////////////////////////////////////////

module fir9 #(parameter N=9)(

output logic signed [10:0] y,

input logic signed [3:0] x,

input logic clk, rst);

//defined in-out variables

logic signed [4:0] c [0:N-1] ='{1,3,8,13,15,13,8,3,1};

logic signed [3:0] storey [0:N-1];

logic signed [10:0] multiy [0:2*N]; //extended array for pipelining

logic signed [10:0] sumy [0:2*N]; //extended array for pipelining

logic clk2, rst2; //clock - increasing drive strength

always_ff@(posedge clk, posedge rst) begin:ffc

clk2<=!clk2;

rst2<=!rst2;

end:ffc

//clock drive strength modification

always_ff@(posedge clk2, posedge rst2)

begin:ff

if(rst2) begin

y<=0;//resetting output to zero

for(int i=0;i<=N-1;i++) begin: a

storey[i]<=0;//resetting all flipflops to 0

multiy[i]<=0;

end:a

end

else begin

storey[0]<=x; // assigning the input to first flipflop

y<=sumy[2*N];//putting the sum out

for(int i=0;i<=N-1;i++) begin

multiy[i]<=storey[i]; // pipelining

sumy[i]<=multiy[i+N]; // pipelining

storey[i+1]<=storey[i];//rippling through flipflops, there is an overflow of one value, but that does not affect anything

end

end

end:ff

always_comb begin:whatever

for(int k=0;k<=N-1;k++)

multiy[k+N]=multiy[k]*c[k];

for(int k=0;k<=N-1;k++)

sumy[N+k+1]=sumy[N+k]+sumy[k];

end:whatever

//summing and multiplying values

endmodule

|

|

|

| Nazaj na vrh |

|

|

hribo

Član

Pridružen-a: Sob 12 Nov 2011 13:38

Prispevkov: 150

Aktiv.: 0.85

Kraj: Domžale

|

Objavljeno: Sob Feb 11, 2012 4:56 pm Naslov sporočila: Objavljeno: Sob Feb 11, 2012 4:56 pm Naslov sporočila: |

|

|

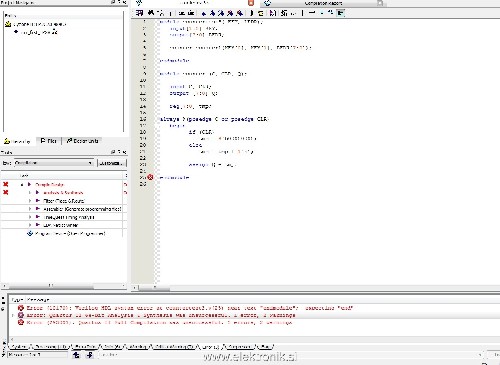

@GopherB tvoje sem spregledal, tole napiše:

Error (10228): Verilog HDL error at countertest3.v(9): module "counter" cannot be declared more than once

Error: Quartus II 64-Bit Analysis & Synthesis was unsuccessful. 1 error, 2 warnings

Error: Peak virtual memory: 369 megabytes

Error: Processing ended: Sat Feb 11 15:39:37 2012

Error: Elapsed time: 00:00:01

Error: Total CPU time (on all processors): 00:00:01

Error (293001): Quartus II Full Compilation was unsuccessful. 3 errors, 2 warnings

_________________

Failing to plan is planning to fail. |

|

| Nazaj na vrh |

|

|

hribo

Član

Pridružen-a: Sob 12 Nov 2011 13:38

Prispevkov: 150

Aktiv.: 0.85

Kraj: Domžale

|

Objavljeno: Sob Feb 11, 2012 8:06 pm Naslov sporočila: Objavljeno: Sob Feb 11, 2012 8:06 pm Naslov sporočila: |

|

|

pa mi je le uspelo.....imel sme dve napaki, in sicer prva je bila end, druga ki je pa bila je pa bila zelo začetniška in sicer imel sem v projektu še eno datoteko napisano v verilogu, ki je tudi imela spremenljivko counter...hvala vsem za pomoč... pa mi je le uspelo.....imel sme dve napaki, in sicer prva je bila end, druga ki je pa bila je pa bila zelo začetniška in sicer imel sem v projektu še eno datoteko napisano v verilogu, ki je tudi imela spremenljivko counter...hvala vsem za pomoč...

_________________

Failing to plan is planning to fail. |

|

| Nazaj na vrh |

|

|

chaos

Član

Pridružen-a: Sob 16 Sep 2006 22:12

Prispevkov: 1063

Aktiv.: 4.46

Kraj: Zagorje ob Savi

|

Objavljeno: Ned Feb 12, 2012 12:29 am Naslov sporočila: Objavljeno: Ned Feb 12, 2012 12:29 am Naslov sporočila: |

|

|

Tale primer je sicer v redu za prve korake, ampak kot prvo uporablja zastarelo sintakso Veriloga, in kot drugo, na neprimeren način uporablja signale - npr. tisti always stavek predstavlja d flip-flop, ki ima priključeno navadno logiko na clock in reset port. Saj delalo bo, ampak to je neprimeren način, sploh za FPGA (omejeno rutanje znotraj čipa).

Svetoval bi ti, da si pogledaš tole stran, ki ima dosti tutorialov in primerov.

Pa še za vzorec, kako bi jaz napisal takšen modul:

| Koda: |

module countertest3 (

input wire clk,

input wire rst,

input wire [1:0] KEY,

output wire [7:0] LEDR

);

reg [1:0] key_sinc0, key_sinc1;

always @ (posedge clk) begin

key_sinc0 <= #1 KEY;

key_sinc1 <= #1 key_sinc0;

end

counter counter1 (

.clk (clk),

.rst (key_sinc1[1]),

.C (key_sinc1[0]),

.Q (LEDR[7:0])

);

endmodule

module counter (

input wire clk,

input wire rst,

input wire C,

input wire CLR,

output reg [7:0] Q

);

always @ (posedge clk, posedge rst) begin

if (rst)

Q <= #1 8'h00;

else if (C)

Q <= #1 tmp + 8'h01;

end

endmodule

|

Pa še hitra razlaga, zakaj tako:

1. najprej sami signali - po imenu sodeč so KEY signali direktni vhodi v FPGA. Takšne signale je potrebno sinhronizirati z urinim ciklom, drugače lahko flip-flopi pridejo v metastabilno stanje. To se preprosto naredi tako, da jih pelješ preko dveh flip-flopov, med katerimi ni nobene logike. V mojem primeru sta to tista dva key_sinc registra.

2. clock (clk) - če v FPGA-ju uporabljaš flip-flope, je preferirano, da uporabljajo nek dejanski urin signal, po možnosti peljan preko internega PLL-a. clock signali grejo namreč znotraj FPGA-ja po globalnem clock routingu, ki je omejen, zato res ni pametno, da uporabljaš kar ene signale za clock. Sicer je to možno, kot je v tem tvojem primeru, ampak ti odsvetujem.

3. način deklaracije modula - že od leta 2001 (Verilog2001 standard) se naj bi porti modula pisali malo drugače, kot je v mojem primeru tisto input wire ... - meni se zdi to dosti bolj pregledno, pa še manj pisanja je - ni potrebno najprej naštevati portov in jih potem še deklarirati ...

4. način instantiacije modula - bolj pametno je uporabljati poimensko instantiacijo - v mojem primeru je to npr. .clk (clk) ... - če boš namreč dodal kakšen port ali zamenjal vrstni red, bi moral v instantiaciji z naštevanjem to na roke popraviti.

5. assignment operator - Verilog pozna dve vrsti assignment operatorjev, en je tako imenovani blocking assignment (=) in non-blocking assignment (<=). V tvojem primeru je napačno uporabljen blocking assignment v always stavku. Na kratko povedano, uporabljaj non-blocking assignment v always stavku, ki v sensitivity listu vsebuje besedo posedge ali negedge, in blocking assignment v vseh drugih primerih.

To je samo nekaj mojih nasvetov, seveda se boš samo odločil, kako boš pisal. Definitivno ti pa svetujem oglede zgoraj omenjene strani.

Pa veliko zabave v svetu FPGA-jev (in čim manj izgubljenih živcev  ! !

LP!

LP!

|

|

| Nazaj na vrh |

|

|

hribo

Član

Pridružen-a: Sob 12 Nov 2011 13:38

Prispevkov: 150

Aktiv.: 0.85

Kraj: Domžale

|

Objavljeno: Ned Feb 12, 2012 10:09 pm Naslov sporočila: Objavljeno: Ned Feb 12, 2012 10:09 pm Naslov sporočila: |

|

|

hvala chaos za res dobro razlago

_________________

Failing to plan is planning to fail. |

|

| Nazaj na vrh |

|

|

|

|

Ne, ne moreš dodajati novih tem v tem forumu

Ne, ne moreš odgovarjati na teme v tem forumu

Ne, ne moreš urejati svojih prispevkov v tem forumu

Ne, ne moreš brisati svojih prispevkov v tem forumu

Ne ne moreš glasovati v anketi v tem forumu

Ne, ne moreš pripeti datotek v tem forumu

Ne, ne moreš povleči datotek v tem forumu

|

Uptime: 232 dni

Powered by phpBB © 2001, 2005 phpBB Group

|