|

www.elektronik.si

Forum o elektrotehniki in računalništvu

|

| Poglej prejšnjo temo :: Poglej naslednjo temo |

| Avtor |

Sporočilo |

commander29

Član

Pridružen-a: Pon 20 Nov 2006 15:24

Prispevkov: 47

Aktiv.: 0.21

|

Objavljeno: Ned Jan 06, 2008 3:46 pm Naslov sporočila: [rešeno]LPC2294 potrebujem pomoč z interrupti Objavljeno: Ned Jan 06, 2008 3:46 pm Naslov sporočila: [rešeno]LPC2294 potrebujem pomoč z interrupti |

|

|

Ima kdo izkušnje s tem procesorjem?

Procesor, ki ga uporabljam je malce star (LPC2294JBD144), in po prebrani dokumentaciji (datasheet, User manual, errates...) in dodanih popravkih kodi, še vedno ne dela noben interrupt. Tukaj je primer Timer 0 interrupta, ki preverjeno dela na LPC2138, LPC2103, LPC2148, tukaj pa ne. Če interrupt vlkopim v kodi potem procesor "zmrzne" (ne vem kaj se z njim dogaja ampak ne gre skozi glavno zanko in ni v interruptni rutini).

V glavni zanki samo xor-am Pin P0.3 v interruptni rutini pa spreminjam P0.0 in ko zaženem program z vključenim interruptom ne miga ne P0.0 in ne P0.3.

Brez interruptov pin P0.3 "miga"

Uporabljam uVision3 z Keil CARM

| Koda: |

#include <LPC22XX.H> // LPC22XX Peripheral Registers

long volatile timeval;

/* Timer Counter 0 Interrupt executes each 10ms @ 60 MHz CPU Clock */

void tc0 (void) __irq {

++timeval;

if (IOPIN0 & 0x00000001) IOCLR0 = 0x00000001; else IOSET0 = 0x00000001;

T0TCR = 0; // Stop Timer0 (Errate)

T0IR = 1; // Clear interrupt flag

T0TCR = 1; // Start Timer0

VICVectAddr = 0; // Acknowledge Interrupt

}

/* Setup the Timer Counter 0 Interrupt */

void init_timer (void) {

T0MR0 = 149999; // 10mSec = 150.000-1 counts

T0MCR = 3; // Interrupt and Reset on MR0

T0TCR = 1; // Timer0 Enable

VICVectAddr0 = (unsigned long)tc0; // set interrupt vector in 0

VICVectCntl0 = 0x20 | 4; // use it for Timer 0 Interrupt

VICIntEnable = 0x00000010; // Enable Timer0 Interrupt

} |

Nazadnje urejal/a commander29 Sob Jan 26, 2008 10:31 pm; skupaj popravljeno 1 krat |

|

| Nazaj na vrh |

|

|

commander29

Član

Pridružen-a: Pon 20 Nov 2006 15:24

Prispevkov: 47

Aktiv.: 0.21

|

Objavljeno: Sob Jan 26, 2008 7:51 am Naslov sporočila: Objavljeno: Sob Jan 26, 2008 7:51 am Naslov sporočila: |

|

|

Ali je kdo na tem forumu delal kaj s tem procesorjem (LPC2292/94)?

Sedaj sem na plato dal novo verzijo tega procesorja z novo masko pa še vedno ne delajo interrupt-i.

|

|

| Nazaj na vrh |

|

|

chaos

Član

Pridružen-a: Sob 16 Sep 2006 22:12

Prispevkov: 1063

Aktiv.: 4.65

Kraj: Zagorje ob Savi

|

Objavljeno: Sob Jan 26, 2008 9:13 am Naslov sporočila: Objavljeno: Sob Jan 26, 2008 9:13 am Naslov sporočila: |

|

|

Prilepi svoj startup.S, boot.S - karkoli že imaš.

LP!

|

|

| Nazaj na vrh |

|

|

commander29

Član

Pridružen-a: Pon 20 Nov 2006 15:24

Prispevkov: 47

Aktiv.: 0.21

|

Objavljeno: Sob Jan 26, 2008 1:15 pm Naslov sporočila: Objavljeno: Sob Jan 26, 2008 1:15 pm Naslov sporočila: |

|

|

| chaos je napisal/a: |

Prilepi svoj startup.S, boot.S - karkoli že imaš.

LP! |

| Koda: |

// Standard definitions of Mode bits and Interrupt (I & F) flags in PSRs

Mode_USR EQU 0x10

Mode_FIQ EQU 0x11

Mode_IRQ EQU 0x12

Mode_SVC EQU 0x13

Mode_ABT EQU 0x17

Mode_UND EQU 0x1B

Mode_SYS EQU 0x1F

I_Bit EQU 0x80 /* when I bit is set, IRQ is disabled */

F_Bit EQU 0x40 /* when F bit is set, FIQ is disabled */

/*

// <h> Stack Configuration (Stack Sizes in Bytes)

// <o0> Undefined Mode <0x0-0xFFFFFFFF:4>

// <o1> Supervisor Mode <0x0-0xFFFFFFFF:4>

// <o2> Abort Mode <0x0-0xFFFFFFFF:4>

// <o3> Fast Interrupt Mode <0x0-0xFFFFFFFF:4>

// <o4> Interrupt Mode <0x0-0xFFFFFFFF:4>

// <o5> User/System Mode <0x0-0xFFFFFFFF:4>

// </h>

*/

UND_Stack_Size EQU 0x00000004

SVC_Stack_Size EQU 0x00000004

ABT_Stack_Size EQU 0x00000004

FIQ_Stack_Size EQU 0x00000004

IRQ_Stack_Size EQU 0x00000080

USR_Stack_Size EQU 0x00000400

AREA STACK, DATA, READWRITE, ALIGN=2

DS (USR_Stack_Size+3)&~3 ; Stack for User/System Mode

DS (SVC_Stack_Size+3)&~3 ; Stack for Supervisor Mode

DS (IRQ_Stack_Size+3)&~3 ; Stack for Interrupt Mode

DS (FIQ_Stack_Size+3)&~3 ; Stack for Fast Interrupt Mode

DS (ABT_Stack_Size+3)&~3 ; Stack for Abort Mode

DS (UND_Stack_Size+3)&~3 ; Stack for Undefined Mode

Top_Stack:

// VPBDIV definitions

VPBDIV EQU 0xE01FC100 /* VPBDIV Address */

/*

// <e> VPBDIV Setup

// <i> Peripheral Bus Clock Rate

// <o1.0..1> VPBDIV: VPB Clock

// <0=> VPB Clock = CPU Clock / 4

// <1=> VPB Clock = CPU Clock

// <2=> VPB Clock = CPU Clock / 2

// <o1.4..5> XCLKDIV: XCLK Pin

// <0=> XCLK Pin = CPU Clock / 4

// <1=> XCLK Pin = CPU Clock

// <2=> XCLK Pin = CPU Clock / 2

// </e>

*/

VPBDIV_SETUP EQU 1

VPBDIV_Val EQU 0x00000001

// Phase Locked Loop (PLL) definitions

PLL_BASE EQU 0xE01FC080 /* PLL Base Address */

PLLCON_OFS EQU 0x00 /* PLL Control Offset*/

PLLCFG_OFS EQU 0x04 /* PLL Configuration Offset */

PLLSTAT_OFS EQU 0x08 /* PLL Status Offset */

PLLFEED_OFS EQU 0x0C /* PLL Feed Offset */

PLLCON_PLLE EQU (1<<0) /* PLL Enable */

PLLCON_PLLC EQU (1<<1) /* PLL Connect */

PLLCFG_MSEL EQU (0x1F<<0) /* PLL Multiplier */

PLLCFG_PSEL EQU (0x03<<5) /* PLL Divider */

PLLSTAT_PLOCK EQU (1<<10) /* PLL Lock Status */

/*

// <e> PLL Setup

// <i> Phase Locked Loop

// <i> CCLK - Processor Clock

// <i> Fcco - PLL Oscillator

// <o1.0..4> MSEL: PLL Multiplier Selection

// <1-32><#-1>

// <i> PLL Multiplier "M" Value

// <i> CCLK = M * Fosc

// <o1.5..6> PSEL: PLL Divider Selection

// <0=> 1 <1=> 2 <2=> 4 <3=> 8

// <i> PLL Divider "P" Value

// <i> Fcco = CCLK * 2 * P

// <i> 156MHz <= Fcco <= 320MHz

// </e>

*/

PLL_SETUP EQU 0

PLLCFG_Val EQU 0x00000024

// Memory Accelerator Module (MAM) definitions

MAM_BASE EQU 0xE01FC000 /* MAM Base Address */

MAMCR_OFS EQU 0x00 /* MAM Control Offset*/

MAMTIM_OFS EQU 0x04 /* MAM Timing Offset */

/*

// <e> MAM Setup

// <i> Memory Accelerator Module

// <o1.0..1> MAM Control

// <0=> Disabled

// <1=> Partially Enabled

// <2=> Fully Enabled

// <i> Mode

// <o2.0..2> MAM Timing

// <0=> Reserved <1=> 1 <2=> 2 <3=> 3

// <4=> 4 <5=> 5 <6=> 6 <7=> 7

// <i> Fetch Cycles

// </e>

*/

MAM_SETUP EQU 0

MAMCR_Val EQU 0x00000002

MAMTIM_Val EQU 0x00000004

// External Memory Controller (EMC) definitions

EMC_BASE EQU 0xFFE00000 /* EMC Base Address */

BCFG0_OFS EQU 0x00 /* BCFG0 Offset */

BCFG1_OFS EQU 0x04 /* BCFG1 Offset */

BCFG2_OFS EQU 0x08 /* BCFG2 Offset */

BCFG3_OFS EQU 0x0C /* BCFG3 Offset */

/*

// <e> External Memory Controller (EMC)

*/

EMC_SETUP EQU 0

/*

// <e> Bank Configuration 0 (BCFG0)

// <o1.0..3> IDCY: Idle Cycles <0-15>

// <o1.5..9> WST1: Wait States 1 <0-31>

// <o1.11..15> WST2: Wait States 2 <0-31>

// <o1.10> RBLE: Read Byte Lane Enable

// <o1.26> WP: Write Protect

// <o1.27> BM: Burst ROM

// <o1.28..29> MW: Memory Width <0=> 8-bit <1=> 16-bit

// <2=> 32-bit <3=> Reserved

// </e>

*/

BCFG0_SETUP EQU 0

BCFG0_Val EQU 0x0000FBEF

/*

// <e> Bank Configuration 1 (BCFG1)

// <o1.0..3> IDCY: Idle Cycles <0-15>

// <o1.5..9> WST1: Wait States 1 <0-31>

// <o1.11..15> WST2: Wait States 2 <0-31>

// <o1.10> RBLE: Read Byte Lane Enable

// <o1.26> WP: Write Protect

// <o1.27> BM: Burst ROM

// <o1.28..29> MW: Memory Width <0=> 8-bit <1=> 16-bit

// <2=> 32-bit <3=> Reserved

// </e>

*/

BCFG1_SETUP EQU 0

BCFG1_Val EQU 0x0000FBEF

/*

// <e> Bank Configuration 2 (BCFG2)

// <o1.0..3> IDCY: Idle Cycles <0-15>

// <o1.5..9> WST1: Wait States 1 <0-31>

// <o1.11..15> WST2: Wait States 2 <0-31>

// <o1.10> RBLE: Read Byte Lane Enable

// <o1.26> WP: Write Protect

// <o1.27> BM: Burst ROM

// <o1.28..29> MW: Memory Width <0=> 8-bit <1=> 16-bit

// <2=> 32-bit <3=> Reserved

// </e>

*/

BCFG2_SETUP EQU 0

BCFG2_Val EQU 0x0000FBEF

/*

// <e> Bank Configuration 3 (BCFG3)

// <o1.0..3> IDCY: Idle Cycles <0-15>

// <o1.5..9> WST1: Wait States 1 <0-31>

// <o1.11..15> WST2: Wait States 2 <0-31>

// <o1.10> RBLE: Read Byte Lane Enable

// <o1.26> WP: Write Protect

// <o1.27> BM: Burst ROM

// <o1.28..29> MW: Memory Width <0=> 8-bit <1=> 16-bit

// <2=> 32-bit <3=> Reserved

// </e>

*/

BCFG3_SETUP EQU 0

BCFG3_Val EQU 0x0000FBEF

/*

// </e> End of EMC

*/

// External Memory Pins definitions

PINSEL2 EQU 0xE002C014 /* PINSEL2 Address */

PINSEL2_Val EQU 0x0E6149E4 /* CS0..3, OE, WE, BLS0..3,

D0..31, A2..23, JTAG Pins */

// Starupt Code must be linked first at Address at which it expects to run.

$IF (EXTMEM_MODE)

CODE_BASE EQU 0x80000000

$ELSEIF (RAM_MODE)

CODE_BASE EQU 0x40000000

$ELSE

CODE_BASE EQU 0x00000000

$ENDIF

AREA STARTUPCODE, CODE, AT CODE_BASE // READONLY, ALIGN=4

PUBLIC __startup

EXTERN CODE32 (?C?INIT)

__startup PROC CODE32

__startup?A:

PUBLIC __startup?A

// Pre-defined interrupt handlers that may be directly

// overwritten by C interrupt functions

EXTERN CODE32 (Undef_Handler?A)

EXTERN CODE32 (SWI_Handler?A)

EXTERN CODE32 (PAbt_Handler?A)

EXTERN CODE32 (DAbt_Handler?A)

EXTERN CODE32 (IRQ_Handler?A)

EXTERN CODE32 (FIQ_Handler?A)

// Exception Vectors

// Mapped to Address 0.

// Absolute addressing mode must be used.

Vectors: LDR PC,Reset_Addr

LDR PC,Undef_Addr

LDR PC,SWI_Addr

LDR PC,PAbt_Addr

LDR PC,DAbt_Addr

NOP /* Reserved Vector */

; LDR PC,IRQ_Addr

LDR PC,[PC, #-0x0FF0] /* Vector from VicVectAddr */

LDR PC,FIQ_Addr

Reset_Addr: DD Reset_Handler

Undef_Addr: DD Undef_Handler?A

SWI_Addr: DD SWI_Handler?A

PAbt_Addr: DD PAbt_Handler?A

DAbt_Addr: DD DAbt_Handler?A

DD 0 /* Reserved Address */

IRQ_Addr: DD IRQ_Handler?A

FIQ_Addr: DD FIQ_Handler?A

// Reset Handler

Reset_Handler:

$IF (EXTMEM_MODE)

LDR R0, =PINSEL2

LDR R1, =PINSEL2_Val

STR R1, [R0]

$ENDIF

IF (EMC_SETUP != 0)

LDR R0, =EMC_BASE

IF (BCFG0_SETUP != 0)

LDR R1, =BCFG0_Val

STR R1, [R0, #BCFG0_OFS]

ENDIF

IF (BCFG1_SETUP != 0)

LDR R1, =BCFG1_Val

STR R1, [R0, #BCFG1_OFS]

ENDIF

IF (BCFG2_SETUP != 0)

LDR R1, =BCFG2_Val

STR R1, [R0, #BCFG2_OFS]

ENDIF

IF (BCFG3_SETUP != 0)

LDR R1, =BCFG3_Val

STR R1, [R0, #BCFG3_OFS]

ENDIF

ENDIF

IF (VPBDIV_SETUP != 0)

LDR R0, =VPBDIV

LDR R1, =VPBDIV_Val

STR R1, [R0]

ENDIF

IF (PLL_SETUP != 0)

LDR R0, =PLL_BASE

MOV R1, #0xAA

MOV R2, #0x55

// Configure and Enable PLL

MOV R3, #PLLCFG_Val

STR R3, [R0, #PLLCFG_OFS]

MOV R3, #PLLCON_PLLE

STR R3, [R0, #PLLCON_OFS]

STR R1, [R0, #PLLFEED_OFS]

STR R2, [R0, #PLLFEED_OFS]

// Wait until PLL Locked

PLL_Loop: LDR R3, [R0, #PLLSTAT_OFS]

ANDS R3, R3, #PLLSTAT_PLOCK

BEQ PLL_Loop

// Switch to PLL Clock

MOV R3, #(PLLCON_PLLE | PLLCON_PLLC)

STR R3, [R0, #PLLCON_OFS]

STR R1, [R0, #PLLFEED_OFS]

STR R2, [R0, #PLLFEED_OFS]

ENDIF

IF (MAM_SETUP != 0)

LDR R0, =MAM_BASE

MOV R1, #MAMTIM_Val

STR R1, [R0, #MAMTIM_OFS]

MOV R1, #MAMCR_Val

STR R1, [R0, #MAMCR_OFS]

ENDIF

// Memory Mapping

MEMMAP EQU 0xE01FC040 /* Memory Mapping Control */

$IF (REMAP)

LDR R0, =MEMMAP

$IF (EXTMEM_MODE)

MOV R1, #3

$ELSEIF (RAM_MODE)

MOV R1, #2

$ELSE

MOV R1, #1

$ENDIF

STR R1, [R0]

$ENDIF

// Setup Stack for each mode

LDR R0, =Top_Stack

// Enter Undefined Instruction Mode and set its Stack Pointer

MSR CPSR_c, #Mode_UND|I_Bit|F_Bit

MOV SP, R0

SUB R0, R0, #UND_Stack_Size

// Enter Abort Mode and set its Stack Pointer

MSR CPSR_c, #Mode_ABT|I_Bit|F_Bit

MOV SP, R0

SUB R0, R0, #ABT_Stack_Size

// Enter FIQ Mode and set its Stack Pointer

MSR CPSR_c, #Mode_FIQ|I_Bit|F_Bit

MOV SP, R0

SUB R0, R0, #FIQ_Stack_Size

// Enter IRQ Mode and set its Stack Pointer

MSR CPSR_c, #Mode_IRQ|I_Bit|F_Bit

MOV SP, R0

SUB R0, R0, #IRQ_Stack_Size

// Enter Supervisor Mode and set its Stack Pointer

MSR CPSR_c, #Mode_SVC|I_Bit|F_Bit

MOV SP, R0

SUB R0, R0, #SVC_Stack_Size

// Enter User Mode and set its Stack Pointer

MSR CPSR_c, #Mode_USR

MOV SP, R0

// Enter the C code

LDR R0,=?C?INIT

TST R0,#1 ; Bit-0 set: INIT is Thumb

LDREQ LR,=exit?A ; ARM Mode

LDRNE LR,=exit?T ; Thumb Mode

BX R0

ENDP

PUBLIC exit?A

exit?A PROC CODE32

B exit?A

ENDP

PUBLIC exit?T

exit?T PROC CODE16

exit: B exit?T

ENDP

END |

|

|

| Nazaj na vrh |

|

|

chaos

Član

Pridružen-a: Sob 16 Sep 2006 22:12

Prispevkov: 1063

Aktiv.: 4.65

Kraj: Zagorje ob Savi

|

Objavljeno: Sob Jan 26, 2008 4:28 pm Naslov sporočila: Objavljeno: Sob Jan 26, 2008 4:28 pm Naslov sporočila: |

|

|

IRQ_Addr: DD IRQ_Handler?A

FIQ_Addr: DD FIQ_Handler?A

Tukaj sta funkciji, ki se kličeta ob FIQ oz IRQ interrupt-u. Imaš te funkcije kje definirane v c-ju? Kaj počnejo?

FIQ_Stack_Size EQU 0x00000004

Če uporabljaš FIQ imaš nastavljen premajhen stack.

LP!

|

|

| Nazaj na vrh |

|

|

commander29

Član

Pridružen-a: Pon 20 Nov 2006 15:24

Prispevkov: 47

Aktiv.: 0.21

|

Objavljeno: Sob Jan 26, 2008 4:44 pm Naslov sporočila: Objavljeno: Sob Jan 26, 2008 4:44 pm Naslov sporočila: |

|

|

| chaos je napisal/a: |

IRQ_Addr: DD IRQ_Handler?A

FIQ_Addr: DD FIQ_Handler?A

Tukaj sta funkciji, ki se kličeta ob FIQ oz IRQ interrupt-u. Imaš te funkcije kje definirane v c-ju? Kaj počnejo?

FIQ_Stack_Size EQU 0x00000004

Če uporabljaš FIQ imaš nastavljen premajhen stack.

LP! |

Če misliš tole:

| Koda: |

#include <LPC22XX.H> // LPC22XX Peripheral Registers

long volatile timeval;

/* Timer Counter 0 Interrupt executes each 10ms @ 60 MHz CPU Clock */

void tc0 (void) __irq {

++timeval;

if (IOPIN0 & 0x00000001) IOCLR0 = 0x00000001; else IOSET0 = 0x00000001;

T0TCR = 0; // Stop Timer0 (Errate)

T0IR = 1; // Clear interrupt flag

T0TCR = 1; // Start Timer0

VICVectAddr = 0; // Acknowledge Interrupt

}

/* Setup the Timer Counter 0 Interrupt */

void init_timer (void) {

T0MR0 = 149999; // 10mSec = 150.000-1 counts

T0MCR = 3; // Interrupt and Reset on MR0

T0TCR = 1; // Timer0 Enable

VICVectAddr0 = (unsigned long)tc0; // set interrupt vector in 0

VICVectCntl0 = 0x20 | 4; // use it for Timer 0 Interrupt

VICIntEnable = 0x00000010; // Enable Timer0 Interrupt

} |

Drugače pa ne vem kaj narediti.

Vedno sem definiral interrupte takole vsaj na LPC2138 in so delali brez težav, tukaj pa ob interruptu se procesor "ustavi" (če debugiram z U-Linkom in dam breakpoint v interruptno routino se ta nikoli ne izvede in ko ustavim procesor je le ta v startup-u.

Kot da nebi vedel kam naprej ob zahtevi po interruptu.....

Če interrupte izklopim procesor živi in dela kar mu "ukažem".

Če rabič se kaj (shemo HW-ja,.....) samo povej, ti jih pošljem,ker tale zadeva me že počasi spravlja ob živce.

Koliko stacka priporočaš za FIQ?

|

|

| Nazaj na vrh |

|

|

Glitch

Član

Pridružen-a: Pet 07 Apr 2006 11:40

Prispevkov: 1477

Aktiv.: 6.30

|

Objavljeno: Sob Jan 26, 2008 6:16 pm Naslov sporočila: Objavljeno: Sob Jan 26, 2008 6:16 pm Naslov sporočila: |

|

|

Tako na hitro pogledano...

Spodaj je prava vrstica iz kode za IRQ, tako da prejsne vprasanje o IRQ rutinah ne pase. Za prekinitve skrbi VIC.

| Citiram: |

| LDR PC,[PC, #-0x0FF0] /* Vector from VicVectAddr */ |

Vseeno je nekaj drugace v kodi ali v nastavitvah, ce pravis da ti koda dela na drugih LPCjih bi moral imeti popolnoma enako kodo.Je to res?

Vem, da so tukaj primeri za IRQ (in z njimi povezani problemi)

http://www.nxp.com/acrobat_download/applicationnotes/AN10414_1.pdf

|

|

| Nazaj na vrh |

|

|

chaos

Član

Pridružen-a: Sob 16 Sep 2006 22:12

Prispevkov: 1063

Aktiv.: 4.65

Kraj: Zagorje ob Savi

|

Objavljeno: Sob Jan 26, 2008 6:25 pm Naslov sporočila: Objavljeno: Sob Jan 26, 2008 6:25 pm Naslov sporočila: |

|

|

Sem spregledal, da uporabljaš VIC. Potem moraš namesto naslova specifične funkcije v naslov za IRQ oz. FIQ prekinitev napisati

ldr pc, [pc,#-0xff0]

Tako se bo zagnala funkcija, katere naslov se bo pojavil v Vector Address Register-ju. Naslov te funkcije pa registriraš v VIC-u.

Stack size nastavi na recimo 0x100.

Edit: vidim, da ti je že Glitch odgovoril ...

Verjetno boš moral še odstraniti I in F zastavice v izbranem načinu procesorja.

LP!

Nazadnje urejal/a chaos Sob Jan 26, 2008 6:28 pm; skupaj popravljeno 1 krat |

|

| Nazaj na vrh |

|

|

Glitch

Član

Pridružen-a: Pet 07 Apr 2006 11:40

Prispevkov: 1477

Aktiv.: 6.30

|

Objavljeno: Sob Jan 26, 2008 6:28 pm Naslov sporočila: Objavljeno: Sob Jan 26, 2008 6:28 pm Naslov sporočila: |

|

|

| chaos, saj ima to napisano. Poglej v kodo, ki jo je pripel. Kar sem citiral je direktno iz te kode.

|

|

| Nazaj na vrh |

|

|

chaos

Član

Pridružen-a: Sob 16 Sep 2006 22:12

Prispevkov: 1063

Aktiv.: 4.65

Kraj: Zagorje ob Savi

|

Objavljeno: Sob Jan 26, 2008 6:30 pm Naslov sporočila: Objavljeno: Sob Jan 26, 2008 6:30 pm Naslov sporočila: |

|

|

Se opravičujem, sem preveč površno bral. Poleg tega zadnje čase ne uporabljam VIC in sem takoj pomislil na direktno klicanje prekinitvenih rutin.

Potem je lahko problem samo še v I in F zastavicah in premajhnem stacku. Najprej povečaj stack ...

LP!

|

|

| Nazaj na vrh |

|

|

Glitch

Član

Pridružen-a: Pet 07 Apr 2006 11:40

Prispevkov: 1477

Aktiv.: 6.30

|

Objavljeno: Sob Jan 26, 2008 6:43 pm Naslov sporočila: Objavljeno: Sob Jan 26, 2008 6:43 pm Naslov sporočila: |

|

|

| Funkcija, ki se izvaja v prekinitvi je sila preprosta, tako da stack ni problem. Si pa omenil se zastavice... v startup kodi je zadnji nacin user, ki pa nima postavljenih zastavic, kar je prav. Ceprav res deluje, kot da do prekinitev sploh ne pride. Res me cudi, da mu napisani program deluje na drugih LPCjih.

|

|

| Nazaj na vrh |

|

|

chaos

Član

Pridružen-a: Sob 16 Sep 2006 22:12

Prispevkov: 1063

Aktiv.: 4.65

Kraj: Zagorje ob Savi

|

Objavljeno: Sob Jan 26, 2008 7:24 pm Naslov sporočila: Objavljeno: Sob Jan 26, 2008 7:24 pm Naslov sporočila: |

|

|

Ja. Res je. Vse štima.

Sem zdaj malo bolj detajlno pogledal ta tvoj primer, pa imaš vse prav nastavljeno, vključno s timerjem.

Zdaj ti pa ne znam več pomagati, ker ne poznam ne te verzije LPC-ja, ne okolja v katerem delaš.

Edino kar mi pride na pamet je, če si slučajno spremenil tabelo prekinitvenih vektorjev, pa tvoj program ne popravi tistega checksuma, ki je tam vmes. Dvomim, da je to problem.

Mogoče bi probal takole: čisto na začetku main nastavi nekaj pinov na nulo, daj neko zakasnitev kar z while zanko, potem enega nastavi na 1, drug pin pa nastavi na ena v prekinitveni rutini. No, saj to že počneš ...

A lahko s tvojim orodjem greš po korakih čez kodo? Kje se procesor obesi oz. skoči nazaj na začetek? Dvomim, da bi se procesor samo zato, ker si omogočil prekinitve, obesil že čisto na začetku, verjetno se pojavi kakšen exception in se procesor takrat obesi.

Bi lahko popravil startup rutino takole:

Namesto:

| Koda: |

Vectors: LDR PC,Reset_Addr

LDR PC,Undef_Addr

LDR PC,SWI_Addr

LDR PC,PAbt_Addr

LDR PC,DAbt_Addr

NOP /* Reserved Vector */

; LDR PC,IRQ_Addr

LDR PC,[PC, #-0x0FF0] /* Vector from VicVectAddr */

LDR PC,FIQ_Addr

Reset_Addr: DD Reset_Handler

Undef_Addr: DD Undef_Handler?A

SWI_Addr: DD SWI_Handler?A

PAbt_Addr: DD PAbt_Handler?A

DAbt_Addr: DD DAbt_Handler?A

DD 0 /* Reserved Address */

IRQ_Addr: DD IRQ_Handler?A

FIQ_Addr: DD FIQ_Handler?A

|

Daj tole:

| Koda: |

Vectors: LDR PC,Reset_Addr

LDR PC,Undef_Addr

LDR PC,SWI_Addr

LDR PC,PAbt_Addr

LDR PC,DAbt_Addr

NOP /* Reserved Vector */

LDR PC,[PC, #-0x0FF0] /* Vector from VicVectAddr */

LDR PC,FIQ_Addr

Reset_Addr: .long Reset_Handler

Undef_Addr: .long undefined_except

Swi_Addr: .long swi_except

Pabt_Addr: .long prefetch_except

Dabt_Addr: .long abort_except

.long 0x00000000 /* Reserved four bytes */

IRQ_Addr: .long irq_except

Fiq_Addr: .long fiq_except

/* Hang the system in case of an interrupt. */

undefined_except: b undefined_except

swi_except: b swi_except

prefetch_except: b prefetch_except

abort_except: b abort_except

irq_except: b irq_except

fiq_except: b fiq_except

|

Tako boš ziher videl, v kateri vrstici se procesor zacikla, pa lahko lažje ugotoviš, kaj je narobe.

LP!

|

|

| Nazaj na vrh |

|

|

commander29

Član

Pridružen-a: Pon 20 Nov 2006 15:24

Prispevkov: 47

Aktiv.: 0.21

|

Objavljeno: Sob Jan 26, 2008 10:31 pm Naslov sporočila: Objavljeno: Sob Jan 26, 2008 10:31 pm Naslov sporočila: |

|

|

ooooooooo ratalo....

Problem ni bil v SW ampak HW. BOOT1 sem mel preko 100k na maso. Kako sovražim ko je zgodi kaj takega po toliko urah vloženega v izdelavo HW pa ti taka malenkost vzame toliko časa.

Seveda ker sem zamenjal procesor prej LPC2294 sedaj LPC2294/01 moram dodati še vse registre ki manjkajo kot posledica izboljšav na maski.

Hvala fantje za pomoč.

Bom pripel slike ko bo končano.

Kar ne razumem je to zakaj je procesor deloval brez vključenih prekinitev kljub nastavljeni BOOT0:BOOT1 na "01" kar pomeni 16 bit vodilo zunanje boot enote (če jaz razumem "datasheet" pravilno.

|

|

| Nazaj na vrh |

|

|

commander29

Član

Pridružen-a: Pon 20 Nov 2006 15:24

Prispevkov: 47

Aktiv.: 0.21

|

Objavljeno: Sre Jul 16, 2008 4:12 pm Naslov sporočila: Objavljeno: Sre Jul 16, 2008 4:12 pm Naslov sporočila: |

|

|

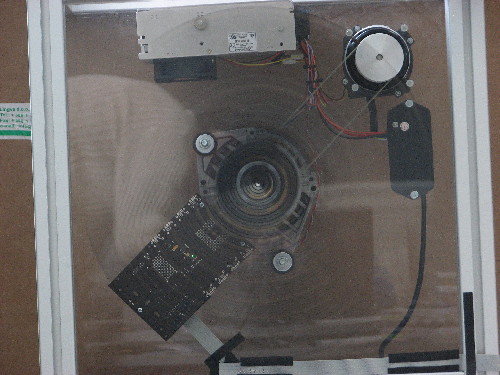

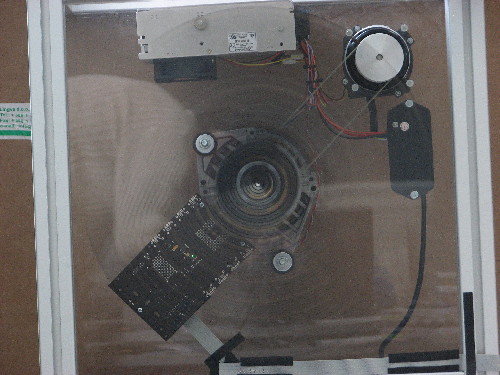

Takole, projekt je končan.

Tukaj pa nekaj rezultatov

| Opis: |

|

| Velikost datoteke: |

973.5 KB |

| Pogledana: |

19 krat |

|

| Opis: |

|

| Velikost datoteke: |

1.33 MB |

| Pogledana: |

17 krat |

|

| Opis: |

|

| Velikost datoteke: |

2.88 MB |

| Pogledana: |

15 krat |

|

|

|

| Nazaj na vrh |

|

|

SimonS

Član

Pridružen-a: Čet 01 Jul 2004 11:18

Prispevkov: 4770

Aktiv.: 20.09

Kraj: Kobarid

|

Objavljeno: Sre Jul 16, 2008 4:55 pm Naslov sporočila: Objavljeno: Sre Jul 16, 2008 4:55 pm Naslov sporočila: |

|

|

Waw, zelo lepo!!!

_________________

Lep dan

Simon |

|

| Nazaj na vrh |

|

|

|

|

Ne, ne moreš dodajati novih tem v tem forumu

Ne, ne moreš odgovarjati na teme v tem forumu

Ne, ne moreš urejati svojih prispevkov v tem forumu

Ne, ne moreš brisati svojih prispevkov v tem forumu

Ne ne moreš glasovati v anketi v tem forumu

Ne, ne moreš pripeti datotek v tem forumu

Ne, ne moreš povleči datotek v tem forumu

|

Uptime: 6 dni

Powered by phpBB © 2001, 2005 phpBB Group

|